#### **GETTING STARTED GUIDE**

# PXIe-1486

#### FlexRIO FPD-Link Interface Module

This document explains how to install and configure the following variants of the PXIe-1486:

- PXIe-1486 FlexRIO FPD-Link<sup>™</sup> Deserializer

- PXIe-1486 FlexRIO FPD-Link<sup>™</sup> Serializer

- PXIe-1486 FlexRIO FPD-Link<sup>™</sup> SerDes

After completing the tasks described in this document, you will have a hardware and driver setup that allows you to design and test your software application.

**Note** If you purchased the PXIe-1486 as part of an NI system, refer to your system documentation for application-specific instructions for using the PXIe-1486.

#### Contents

| FlexRIO Documentation and Resources.                               | 2 |

|--------------------------------------------------------------------|---|

| Preparing the System Components                                    |   |

| Unpacking the Kit                                                  |   |

| Verifying the Kit Contents                                         |   |

|                                                                    |   |

| System Components                                                  |   |

| Prerequisites                                                      |   |

| Verifying the System Requirements                                  |   |

| Installing the Software                                            | 4 |

| Installing the PXIe-1486                                           | 4 |

| Cabling the PXIe-1486                                              | 4 |

| Configuring the PXIe-1486 in MAX                                   | 8 |

| Accessing FlexRIO with Integrated I/O Examples                     | 9 |

| Common FlexRIO with Integrated I/O Examples                        | 0 |

| Component-Level Intellectual Property (CLIP)                       |   |

| Front Panels, Connectors, and Block Diagrams                       | 1 |

| PXIe-1486 Deserializer Front Panel, Connectors, and Block Diagram1 | 1 |

| PXIe-1486 Serializer Front Panel, Connectors, and Block Diagram1   | 4 |

| PXIe-1486 SerDes Front Panel, Connectors, and Block Diagram 1      | 7 |

| FPGA Carrier Block Diagram                                         | 0 |

| Where to Go Next                                                   |   |

| NI Services. 2                                                     | 0 |

## FlexRIO Documentation and Resources

Use the following resources to find more information about the PXIe-1486.

All product documentation can be found at *ni.com/manuals* or in LabVIEW by clicking **Help**.

Table 1. FlexRIO Documentation and Resources

| Document                                                          | Contents                                                                                                                                                                   |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PXIe-1486 Getting Started Guide (this document)                   | Installation instructions     Basic programming instructions                                                                                                               |

| PXIe-1486 Specifications                                          | <ul> <li>Operating environment requirements</li> <li>IO specifications</li> <li>Clocking specifications</li> <li>Physical and mechanical specifications</li> </ul>         |

| PXIe-1486 Safety,<br>Environmental, and Regulatory<br>Information | Safety and compliance information     Environmental information                                                                                                            |

| LabVIEW FPGA Module Help                                          | Basic functionality of the FPGA module     Instructions for developing and debugging custom hardware logic                                                                 |

| NI-FlexRIO Readme                                                 | <ul> <li>Minimum system requirements</li> <li>Supported Application Development Environments (ADEs)</li> <li>Known issues and bug fixes</li> <li>Recent updates</li> </ul> |

| FlexRIO Help                                                      | <ul> <li>Hardware reference information</li> <li>Programming instructions</li> <li>I/O Component Level IP (CLIP) development information</li> </ul>                        |

| LabVIEW Examples                                                  | Examples showing how to run FPGA VIs on your device     How showing how to run host VIs on your device                                                                     |

| FlexRIO product page                                              | <ul><li>Product information</li><li>Data sheets</li></ul>                                                                                                                  |

### Preparing the System Components

### Unpacking the Kit

**Notice** To prevent electrostatic discharge (ESD) from damaging the device, ground yourself using a grounding strap or by holding a grounded object, such as your computer chassis.

- Touch the antistatic package to a metal part of the computer chassis. 1.

- 2. Remove the device from the package and inspect the device for loose components or any other sign of damage.

**Notice** Never touch the exposed pins of connectors.

**Note** Do not install a device if it appears damaged in any way.

Unpack any other items and documentation from the kit.

Store the device in the antistatic package when the device is not in use.

### Verifying the Kit Contents

Verify that the following items are included in the PXIe-1486 kit.

Figure 1. Kit Contents

- 3. PXIe-1486 Safety, Environmental, and Regulatory Information

- 4. PXIe-1486 Getting Started Guide (This Document)

### System Components

The PXIe-1486 is intended for use with the following system components.

#### Required System Components

- PXIe chassis with slot cooling capacity ≥58 W

- Camera or serial device (for Deserializer or SerDes modules)

<sup>1.</sup> PXIe-1486 Module 2 Terminal blocks

- Engine control unit (for Serializer or SerDes modules)

- PXI Express embedded controller or PC with MXI controller system

#### **Optional System Components**

- Power source (for Deserializer or SerDes modules)

- Power sink (for Serializer or SerDes modules)

- Copper power connector wire

- FAKRA Female Code Z to FAKRA Female Code Z Cable(s)

**Note** See the *PXIe-1486 Specifications* for detailed information on compatible serial devices, chassis, copper connector wire, and other system components.

### **Prerequisites**

## Verifying the System Requirements

To use the FlexRIO instrument driver, your system must meet certain requirements.

Refer to the product readme, which is available online on the driver software download page or at *ni.com/manuals*, for more information about minimum system requirements, recommended system, and supported application development environments (ADEs).

## Installing the Software

Download the following software from ni.com/downloads.

**Note** NI software includes NI Package Manager to handle the installation. Refer to the NI Package Manager Manual at *ni.com/r/nipmmanual* for more information about installing, removing, and upgrading NI software using NI Package Manager.

- LabVIEW

- LabVIEW FPGA Module

- FlexRIO

## Installing the PXIe-1486

For instructions on how to install your PXIe-1486 into the chassis, refer to your chassis documentation, available at *ni.com/manuals*.

## Cabling the PXIe-1486

Complete the following steps to connect your PXIe-1486 to other system components.

Connect your chassis to a power source as described in the chassis Getting Started Guide.

- Connect serial device(s) and ECU(s) as required for your application. 2.

- For Deserializer or SerDes modules, use a FAKRA cable to connect serial device(s) to the PXIe-1486 serial input (SI) connector(s).

- For Serializer or SerDes modules, use a FAKRA cable to connect ECU(s) to the PXIe-1486 serial output (SO) connector(s).

**Note** Serial output and serial input coaxial connectors on the PXIe-1486 are physically identical. They can be differentiated by their labels. Serial output channels are labeled SO and serial input connectors are labeled SI.

- Connect the terminal blocks included in your kit to the AUX power connectors on the PXIe-1486.

- (Optional) Connect power sink(s) or power source(s) to the AUX power connectors as 4. required for your application.

- For Deserializer or SerDes modules, use a copper conductor wire to connect a power source to the serial input channel's corresponding pin on the AUX power connector.

- This allows you to supply external power. If you do not connect an external power source, devices connected to PXIe-1486 can be powered by the chassis backplane.

- For Serializer or SerDes modules, use a copper conductor wire to connect a power b) sink to the serial output channel's corresponding pin on the AUX power connector.

This allows you to simulate an additional load.

Note AUX power connector pins map to serial input and serial output connectors one to one.

Refer to the following diagrams for examples of cabled configurations.

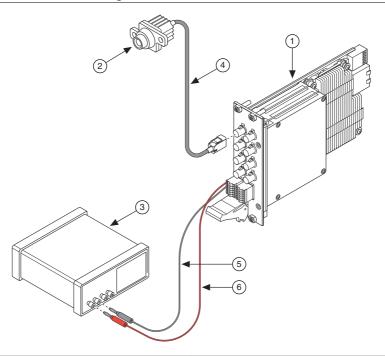

Figure 2. PXIe-1486 Deserializer

- 1. PXIe-1486 Deserializer Module

- 2. Camera or Serial Device

- 3. Power Source

- 4. FAKRA Female Code Z to Serial Device Connector Cable

- 5. Power Connector Wire, Grounding

- 6. Power Connector Wire, Positively Charged

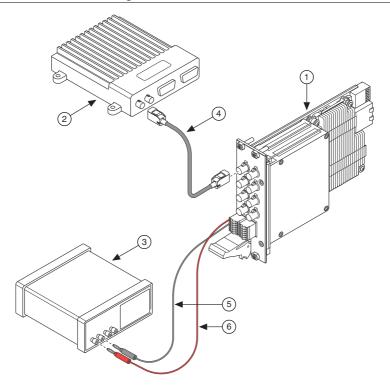

- 1. PXIe-1486 Serializer Module

- 2. Engine Control Unit (ECU)

- 3. Power Sink

- 4. FAKRA Female Code Z to FAKRA Female Code Z Cable

- 5. Power Connector Wire, Grounding

- 6. Power Connector Wire, Positively Charged

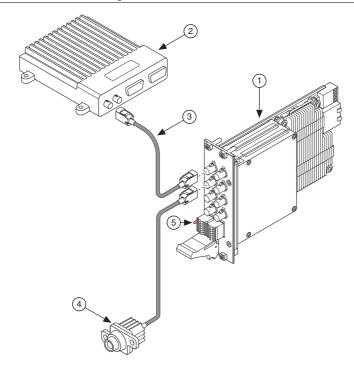

- 1. PXIe-1486 SerDes Module

- 2. Engine Control Unit (ECU)

- 3. FAKRA Female Code Z to FAKRA Female Code Z Cable

- 4. Camera or Serial Device

- 5. Power Connector Wire, Positively Charged

**Note** In the PXIe-1486 SerDes module configuration shown, the power connector wire allows the ECU to power the camera or serial device.

#### **Related Information**

PXIe-1486 Deserializer Front Panel, Connectors, and Block Diagram on page 11

PXIe-1486 Serializer Front Panel, Connectors, and Block Diagram on page 14

PXIe-1486 SerDes Front Panel, Connectors, and Block Diagram on page 17

## Configuring the PXIe-1486 in MAX

Use Measurement & Automation Explorer (MAX) to configure your NI hardware. MAX informs other programs about which NI hardware products are in the system and how they are configured. MAX is automatically installed with FlexRIO.

Launch MAX.

In the configuration tree, expand Devices and Interfaces to see the list of installed NI hardware.

Installed modules appear under the name of their associated chassis.

Expand your Chassis tree item.

MAX lists all modules installed in the chassis. Your default names may vary.

**Note** If you do not see your module listed, press <F5> to refresh the list of installed modules. If the module is still not listed, power off the system, ensure the module is correctly installed, and restart.

- Record the identifier MAX assigns to the hardware. Use this identifier when programming the PXIe-1486.

- Self-test the hardware by selecting the item in the configuration tree and clicking Self-5. **Test** in the MAX toolbar.

The MAX self-test performs a basic verification of hardware resources.

## Accessing FlexRIO with Integrated I/O **Examples**

The NI-FlexRIO driver includes several example applications for LabVIEW. These examples serve as interactive tools, programming models, and as building blocks in your own applications. Complete the following steps to access all FlexRIO with Integrated I/O getting started examples.

- In LabVIEW, click Help »Find Examples .

- In the NI Example Finder window that opens, click Hardware Input and Output » FlexRIO »Integrated IO »Getting Started .

- 3. Double click Getting Started with FlexRIO Integrated IO.vi.

The FlexRIO with Integrated IO Project Creator window will open.

Select the example that corresponds to the name of your FlexRIO module. The **Description** window includes a short description of the getting started example for your device. Rename the project, select a location for this project, and click **OK**.

The **Project Explorer** window for your new project opens.

Online examples are also available to demonstrate FlexRIO basics, such as using DRAM, acquiring data, and performing high throughput streaming. To access these examples, search FlexRIO examples in the Search the community field at ni.com/examples.

#### Common FlexRIO with Integrated I/O Examples

In addition to the examples within the FlexRIO with Integrated IO Project Creator, NI provides several examples that apply to all FlexRIO with Integrated I/O modules to help you perform common tasks.

The following examples can be found in the NI Example Finder:

- Show All FlexRIO with Integrated IO Hardware.vi queries and displays a set of hardware properties from all FlexRIO with Integrated I/O devices in a chassis.

- Vivado Export Getting Started Ultrascale.lvproj demonstrates the use of the Vivado Project Export feature.

- Read-Write Calibration Data.vi demonstrates how to read and write calibration data and metadata into the storage space of FlexRIO with Integrated I/O devices.

### Component-Level Intellectual Property (CLIP)

The LabVIEW FPGA Module includes component-level intellectual property (CLIP) for HDL IP integration. FlexRIO devices support two types of CLIP: user-defined and socketed.

- User-defined CLIP allows you to insert HDL IP into an FPGA target, enabling VHDL code to communicate directly with an FPGA VI.

- Socketed CLIP provides the same IP integration of the user-defined CLIP, but it also allows the CLIP to communicate directly with circuitry external to the FPGA. Adapter module socketed CLIP allows your IP to communicate directly with both the FPGA VI and the external adapter module connector interface.

The PXIe-1486 ships with socketed CLIP items that add module I/O to the LabVIEW project.

## Front Panels, Connectors, and Block Diagrams

## PXIe-1486 Deserializer Front Panel, Connectors, and **Block Diagram**

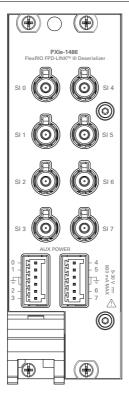

Figure 5. PXIe-1486 Deserializer Front Panel

Table 2. PXIe-1486 Deserializer Front Panel Connectors Signal Descriptions

| Signal Name | Description                           | FlexRIO Terminal Name |

|-------------|---------------------------------------|-----------------------|

| SI 0        | Serial input to internal deserializer | SI0                   |

| SI 1        | Serial input to internal deserializer | SI1                   |

| SI 2        | Serial input to internal deserializer | SI2                   |

| SI 3        | Serial input to internal deserializer | SI3                   |

Table 2. PXIe-1486 Deserializer Front Panel Connectors Signal Descriptions (Continued)

| Signal Name | Description                           | FlexRIO Terminal Name |

|-------------|---------------------------------------|-----------------------|

| SI 4        | Serial input to internal deserializer | SI4                   |

| SI 5        | Serial input to internal deserializer | SI5                   |

| SI 6        | Serial input to internal deserializer | SI6                   |

| SI 7        | Serial input to internal deserializer | SI7                   |

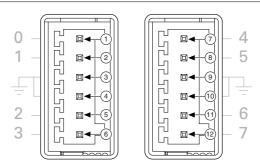

Figure 6. PXIe-1486 Deserializer AUX Power Connectors

Table 3. PXIe-1486 Descriptions Table 3. PXIe-1486 Descriptions

| Signal Pin | Description                   |

|------------|-------------------------------|

| 1          | Power supply for channel SI 0 |

| 2          | Power supply for channel SI 1 |

| 3          | Digital/chassis grounding     |

| 4          | Digital/chassis grounding     |

| 5          | Power supply for channel SI 2 |

| 6          | Power supply for channel SI 3 |

| 7          | Power supply for channel SI 4 |

| 8          | Power supply for channel SI 5 |

| 9          | Digital/chassis grounding     |

| 10         | Digital/chassis grounding     |

Table 3. PXIe-1486 Deserializer AUX Power Connectors Signal Descriptions (Continued)

| Signal Pin | Description                   |

|------------|-------------------------------|

| 11         | Power supply for channel SI 6 |

| 12         | Power supply for channel SI 7 |

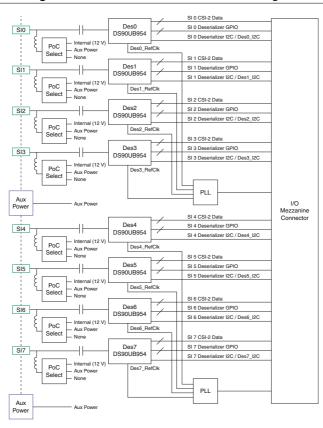

Figure 7. PXIe-1486 Deserializer I/O Block Diagram

## PXIe-1486 Serializer Front Panel, Connectors, and **Block Diagram**

Figure 8. PXIe-1486 Serializer Front Panel

Table 4. PXIe-1486 Serializer Front Panel Connectors Signal Descriptions

| Signal Name | Description                            | FlexRIO Terminal Name |

|-------------|----------------------------------------|-----------------------|

| SO 0        | Serial output from internal serializer | SO0                   |

| SO 1        | Serial output from internal serializer | SO1                   |

| SO 2        | Serial output from internal serializer | SO2                   |

| SO 3        | Serial output from internal serializer | SO3                   |

| SO 4        | Serial output from internal serializer | SO4                   |

| SO 5        | Serial output from internal serializer | SO5                   |

Table 4. PXIe-1486 Serializer Front Panel Connectors Signal Descriptions (Continued)

| Signal Name | Description                            | FlexRIO Terminal Name |

|-------------|----------------------------------------|-----------------------|

| SO 6        | Serial output from internal serializer | SO6                   |

| SO 7        | Serial output from internal serializer | SO7                   |

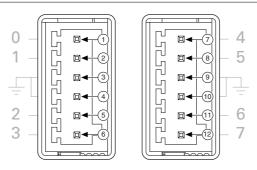

Figure 9. PXIe-1486 Serializer AUX Power Connectors

Table 5. PXIe-1486 Serializer AUX Power Connectors Signal Descriptions

| Signal Pin | Description                 |

|------------|-----------------------------|

| 1          | Power sink for channel SO 0 |

| 2          | Power sink for channel SO 1 |

| 3          | Digital/chassis grounding   |

| 4          | Digital/chassis grounding   |

| 5          | Power sink for channel SO 2 |

| 6          | Power sink for channel SO 3 |

| 7          | Power sink for channel SO 4 |

| 8          | Power sink for channel SO 5 |

| 9          | Digital/chassis grounding   |

| 10         | Digital/chassis grounding   |

| 11         | Power sink for channel SO 6 |

| 12         | Power sink for channel SO 7 |

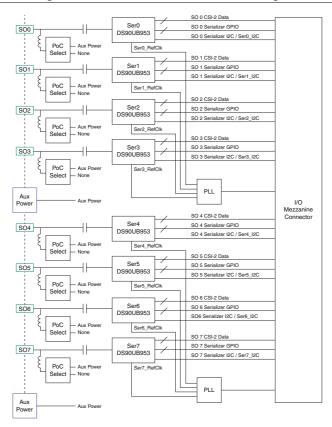

Figure 10. PXIe-1486 Serializer I/O Block Diagram

## PXIe-1486 SerDes Front Panel, Connectors, and Block Diagram

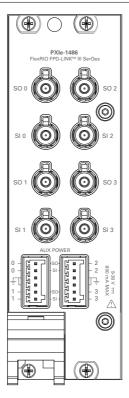

Figure 11. PXIe-1486 SerDes Front Panel

Table 6. PXIe-1486 SerDes Front Panel Connectors Signal Descriptions

| Signal Name | Description                            | FlexRIO Terminal Name |

|-------------|----------------------------------------|-----------------------|

| SO 0        | Serial output from internal serializer | SO0                   |

| SI 0        | Serial input to internal deserializer  | SI0                   |

| SO 1        | Serial output from internal serializer | SO1                   |

| SI 1        | Serial input to internal deserializer  | SI1                   |

| SO 2        | Serial output from internal serializer | SO2                   |

| SI 2        | Serial input to internal deserializer  | SI2                   |

Table 6. PXIe-1486 SerDes Front Panel Connectors Signal Descriptions (Continued)

| Signal Name | Description                            | FlexRIO Terminal Name |

|-------------|----------------------------------------|-----------------------|

| SO 3        | Serial output from internal serializer | SO3                   |

| SI 3        | Serial input to internal deserializer  | SI3                   |

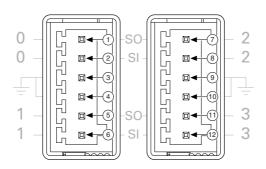

Figure 12. PXIe-1486 SerDes AUX Power Connectors

Table 7. PXIe-1486 SerDes AUX Power Connectors Signal Descriptions

| Signal Pin | Description                   |

|------------|-------------------------------|

| 1          | Power sink for channel SO 0   |

| 2          | Power supply for channel SI 0 |

| 3          | Digital/chassis grounding     |

| 4          | Digital/chassis grounding     |

| 5          | Power sink for channel SO 1   |

| 6          | Power supply for channel SI 1 |

| 7          | Power sink for channel SO 2   |

| 8          | Power supply for channel SI 2 |

| 9          | Digital/chassis grounding     |

| 10         | Digital/chassis grounding     |

| 11         | Power sink for channel SO 3   |

| 12         | Power supply for channel SI 3 |

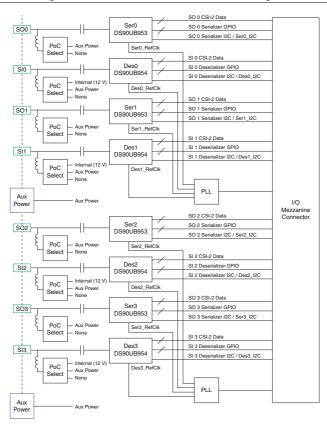

Figure 13. PXIe-1486 SerDes I/O Block Diagram

### FPGA Carrier Block Diagram

+1.8 V Power Supplies +12 V Flash +12 V, +3.3 V Gen3 x8 PCle DStarB, DStarC //O Mezzanine Connector Single Ended GPIO **PXI** Triggers **FPGA** Differential GPIO Module Clocking PXIe\_CLK100 PXI CLK10 Synchronization Clock 0 DRAM† DRAM<sup>1</sup> Bank 0 Bank 1

Figure 14. PXIe-1486 FPGA Block Diagram

#### Where to Go Next

Before you can use your system, you need to configure the connection between the serial device and the PXIe-1486, build your application, then test and troubleshoot your application.

Contact NI for more information about developing the software resources to operate your system. See *FlexRIO Documentation and Resources* for additional information.

#### **NI Services**

Visit *ni.com/support* to find support resources including documentation, downloads, and troubleshooting and application development self-help such as tutorials and examples.

Visit *ni.com/services* to learn about NI service offerings such as calibration options, repair, and replacement.

Visit ni.com/register to register your NI product. Product registration facilitates technical support and ensures that you receive important information updates from NI.

NI corporate headquarters is located at 11500 N Mopac Expwy, Austin, TX, 78759-3504, USA.

Information is subject to change without notice. Refer to the NI Trademarks and Logo Guidelines at ni.com/trademarks for information on NI trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering NI products/technology, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your media, or the National Instruments Patent Notice at ni.com/patents. You can find information about end-user license agreements (EULAs) and third-party legal notices in the readme file for your NI product. Refer to the Export Compliance Information at ni.com/legal/export-compliance for the NI global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data. NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS. U.S. Government Customers: The data contained in this manual was developed at private expense and is subject to the applicable limited rights and restricted data rights as set forth in FAR 52.227-14, DFAR 252.227-7014, and DFAR 252.227-7015. © 2020 National Instruments Corporation. All rights reserved.